# OpenPiton in Action

**Princeton University**

http://openpiton.org

# **Extension Using NoCs**

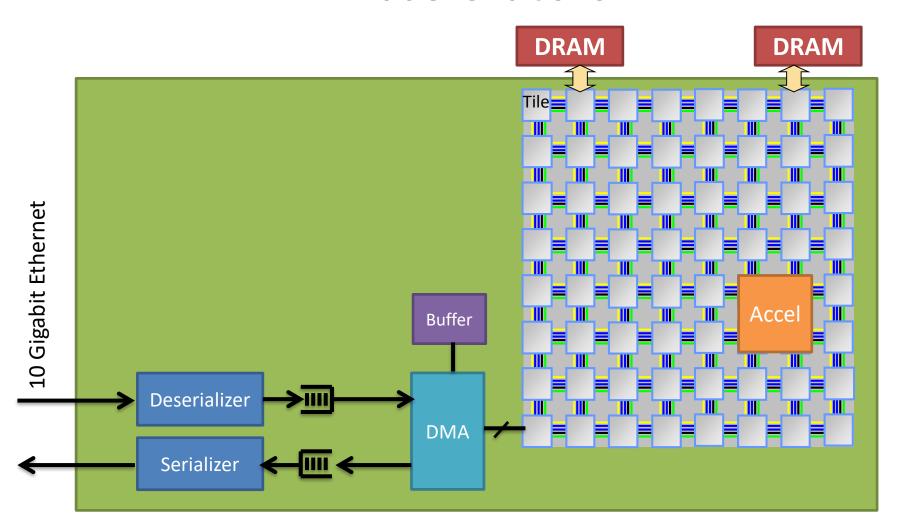

# P-Mesh NoC Connected I/O and Accelerators

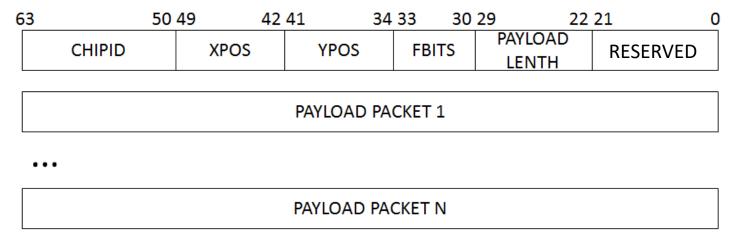

#### P-Mesh NoC: packet format

CHIPID: Highest bits indicate whether the destination is onchip or off-chip, the rest of the bits indicates the chip ID

XPOS: The position of the destination tile in the X dimension

YPOS: The position of the destination tile in the Y dimension

FBITS: The router output port to the destination

PAYLOAD LENGTH: The number of payload packets

RESERVED: Reserved Bits used by higher-level protocols.

#### P-Mesh NoC: .h files

```

piton/design/include/network_define.h

Defines the header flits b63-22

(all except messageid, tag, and options 1)

```

piton/design/include/define.vh defines the rest

```

181 //Memory requests from L2 to DRAM

182 `define MSG_TYPE_LOAD_MEM 8'd19

183 `define MSG_TYPE_STORE_MEM 8'd20

184

```

```

`define MSG TYPE RESERVED

8'd0

8'd31

`define MSG TYPE LOAD REQ

define MSG TYPE PREFETCH REQ

8'd1

'define MSG TYPE STORE REQ

8'd2

define MSG TYPE BLK STORE REQ

8'd3

define MSG TYPE BLKINIT STORE REQ

8'd4

`define MSG TYPE CAS REQ

8'd5

`define MSG TYPE CAS P1 REQ

8'd6

define MSG TYPE CAS P2Y REQ

8'd7

`define MSG TYPE CAS P2N REQ

8'd8

`define MSG TYPE SWAP REQ

8'd9

`define MSG TYPE SWAP P1 REQ

8'd10

`define MSG TYPE SWAP P2 REQ

8'd11

`define MSG TYPE WB REQ

8'd12

8'd13

`define MSG TYPE WBGUARD REQ

`define MSG TYPE NC LOAD REQ

8'd14

`define MSG TYPE NC STORE REQ

8'd15

define MSG TYPE INTERRUPT FWD

8'd32

```

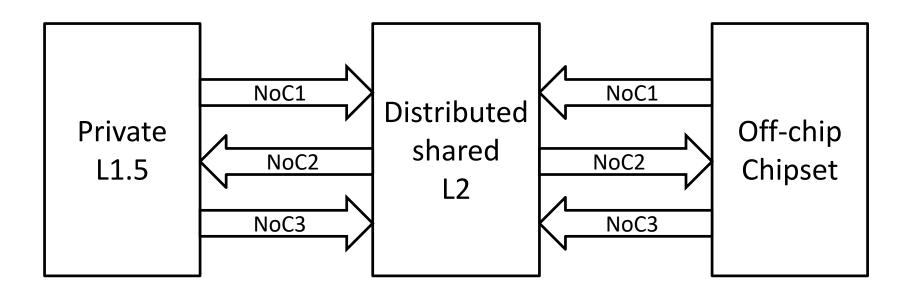

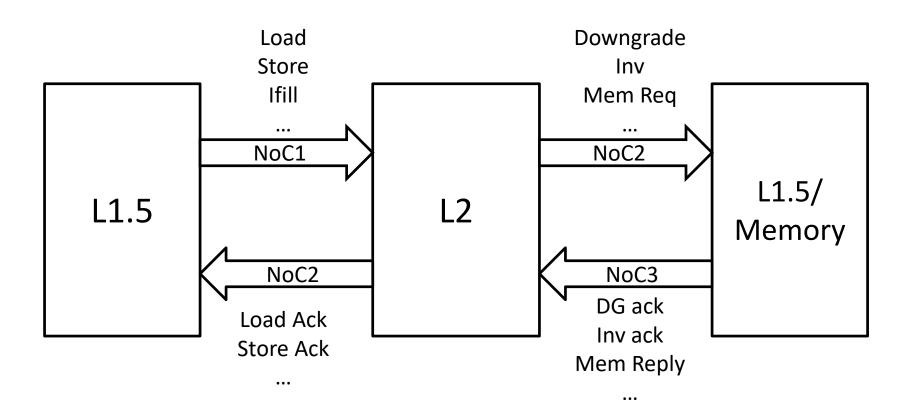

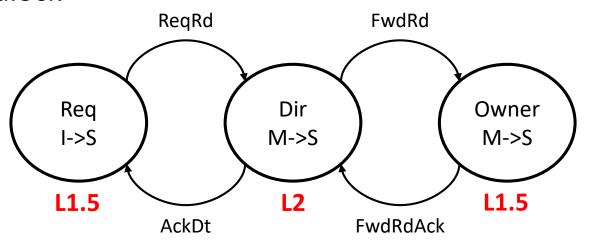

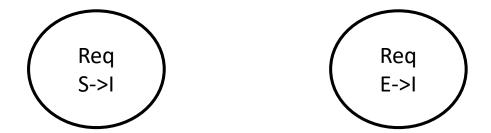

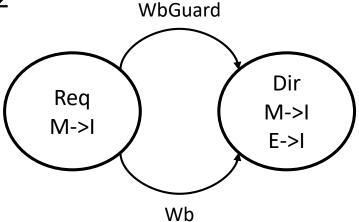

#### Cache Coherence Protocol

#### Directory-based MESI coherence Protocol

- Four-hop message communication (no direct communication between private L1.5 caches)

- Uses 3 physical NoCs with point-to-point ordering to avoid deadlock

- The directory and L2 are co-located but state information are maintained separately

- Silent eviction in E and S states

- No need for acknowledgement upon write-back of dirty lines from L1.5 to L2, but writeback guard needed in some cases.

## Memory Hierarchy Datapath

#### **NoC** Messages

In order to avoid deadlock, NoC3 messages will never be blocked

8

# **Backup Slides**

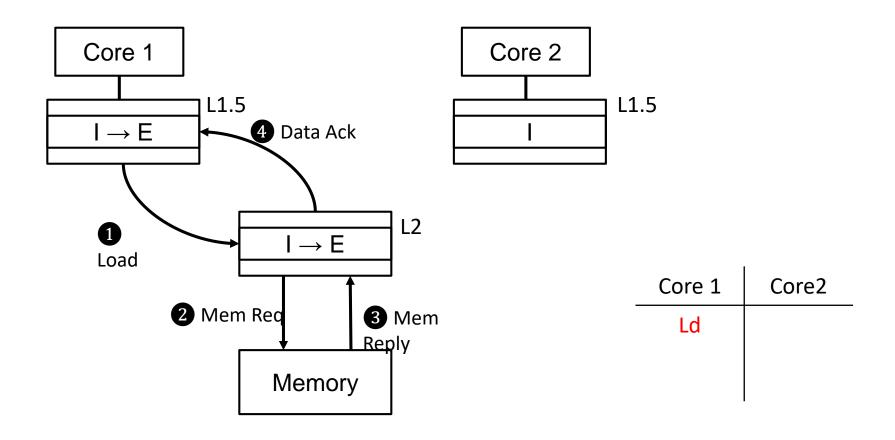

#### **Coherence Transaction Example**

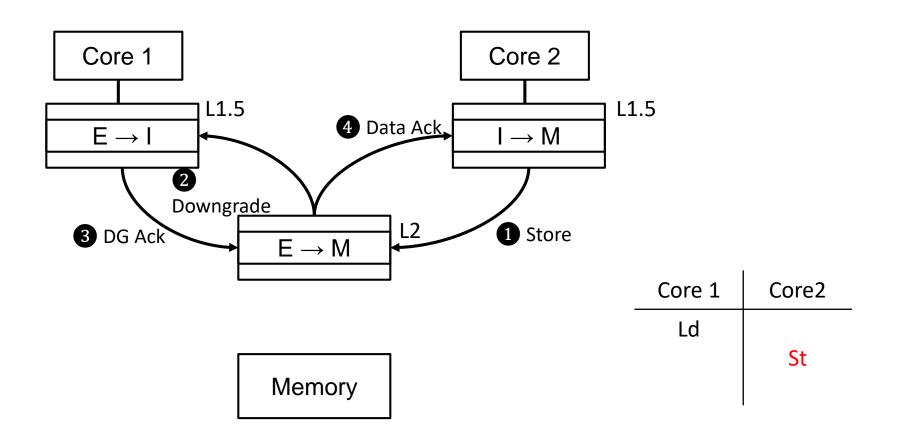

## Coherence Transaction Example (2)

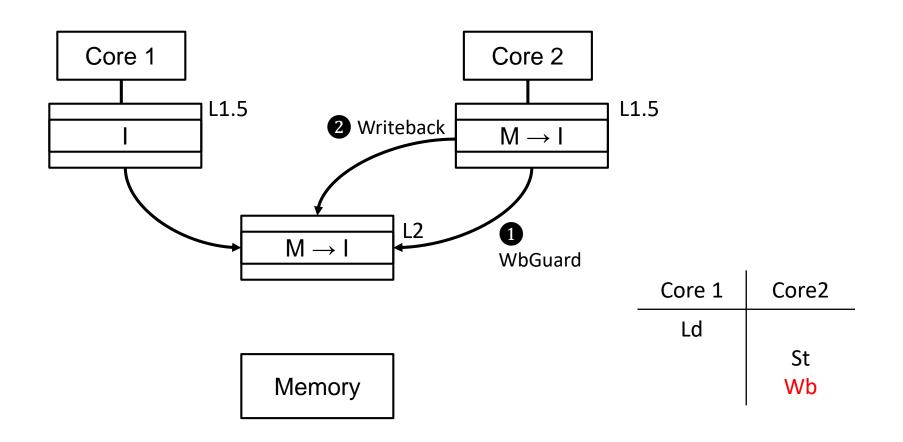

## Coherence Transaction Example (3)

#### Adding to OpenPiton

- AXI-Lite

- Wishbone

- Interfacing with the Network on Chip

## Hooking up an AXI-Lite device

#### Interfacing with the Networks-on-Chip

- 1.Packet format

- Highlighting key packet fields

- 2. Definition files

- h files

- 3.Instantiations in Verilog design

#### NoC: packet format

```

64-bit flits

1 packet header (64b) + X packet payload flits

(64b * X)

Ex: Cache request from L1.5 to L2

Header flit + req. address flit + metadata

flit

Ex: Cache response from L2 to L1.5

Header flit + 2x data flits (16B cache line)

Ex: Instruction cache response

Header flit + 4x data flits (32B cache line)

```

#### **NoC:** instantiations

piton/design/chip/rtl/chip.v.pyv

Chip-wide connections between tiles

Auto generated using PYHP

```

# generate wires

if (NETWORK CONFIG == "xbar config"):

for i in range(X TILES + 1):

for k in [1,2,3]:

print "wire [`DATA WIDTH-1:0] xbar %d out noc%d data;" % (i, k)

print "wire xbar %d out noc%d valid;" % (i, k)

print "wire xbar %d out noc%d yummy;" % (i, k)

for i in range(X TILES):

for j in range(Y TILES):

for k in [1,2,3]:

print "wire [`DATA WIDTH-1:0] tile %d %d out noc%d data;" % (j,i,k)

print "wire tile %d %d out noc%d valid;" % (j,i,k)

print "wire tile %d %d out noc%d yummy;" % (j,i,k)

# make offchip signals

for k in [1,2,3]:

print "wire ['DATA WIDTH-1:0] offchip out noc%d data;" % (k)

print "wire offchip out noc%d valid;" % (k)

print "wire offchip out noc%d yummy;" % (k)

```

#### **NoC:** instantiations

piton/design/chip/tile/rtl/tile.v.pyv Instantiation of NoC1/2/3

```

dynamic node top wrap user dynamic network0

(.clk(clk gated),

.reset in(~rst n f),

.dataIn N(dyn0 dataIn N),

.dataIn E(dyn0 dataIn E),

.dataIn S(dyn0 dataIn S),

.dataIn W(dyn0 dataIn W),

.dataIn P(buffer router data noc1),

.validIn N(dyn0 validIn N),

.validIn E(dyn0 validIn E),

.validIn S(dvn0 validIn S),

.validIn W(dyn0 validIn W),

.validIn P(buffer router_valid_noc1),

.yummyIn N(dyn0 dNo yummy),

.yummyIn E(dyn0 dEo yummy),

.yummyIn S(dyn0 dSo yummy),

.yummyIn W(dyn0 dWo yummy),

.yummyIn P(buffer router yummy noc1),

.myLocX(config coreid x),

.myLocY(config coreid y),

.myChipID(config chipid),

```

piton/design/chip/tile/rtl/tile.v.pyv

Selectable between router and

crossbar design

```

if (NETWORK CONFIG == "xbar config"):

S = '''

assign dyn0 do = buffer router data noc1;

assign dyn0 do valid = buffer router valid noc1;

assign dyn0 yummyOut = buffer router yummy noc1;

assign router buffer data noc1 = dyn0 dataIn;

assign router buffer data val noc1 = dyn0 validIn;

assign router buffer consumed noc1 = dyn0 do yummy;

assign dyn1 do = buffer router data noc2;

assign dyn1 do valid = buffer router valid noc2;

assign dyn1 yummyOut = buffer router yummy noc2;

assign router buffer data noc2 = dyn1 dataIn;

assign router buffer data val noc2 = dyn1 validIn;

assign router buffer consumed noc2 = dyn1 do yummy;

assign dyn2 do = buffer router data noc3;

assign dyn2 do valid = buffer router valid noc3;

assign dyn2 yummyOut = buffer router yummy noc3;

assign router buffer data noc3 = dyn2 dataIn;

assign router buffer data val noc3 = dyn2 validIn;

assign router buffer consumed noc3 = dyn2 do yummy;

print s

```

#### Cache Coherence Protocol

#### Directory-based MESI coherence Protocol

- Four-hop message communication (no direct communication between private L1.5 caches)

- Uses 3 physical NoCs with point-to-point ordering to avoid deadlock

## Cache Coherence Protocol (2)

Directory-based MESI coherence Protocol

The directory and L2 are co-located but state information are maintained separately

| L2 State | Dir State | Tag | Data | Sharer List |

|----------|-----------|-----|------|-------------|

|          |           |     |      |             |

|          |           |     |      |             |

• • •

## Cache Coherence Protocol (3)

Directory-based MESI coherence Protocol

Silent eviction in E and S states

No need for acknowledgement upon write-back of dirty lines from L1.5 to L2

#### Example: Add an on-chip accelerator

- 1. Implement the NoC interface for the accelerator

- 2. Design and implement the control flow for the accelerator

- Use interrupt packets to init and stop the accelerator

- Use special load and stores to config the accelerator

- Follow the coherence protocol if a coherence cache is maintained

- 3. Connect the accelerator to NoCs and assign it a new tile ID

- 4. Modify the OS code to init the accelerator if needed

- 5. Write tests to test the accelerator