Intuitive Python API

PRGA is written in Python with an intuitive, modularized, and highly extensible API. Enjoy the smoothness of developing in a high-level programming language!

Templated File Generation

PRGA generates most files based on parameterized Jinja templates. Feel free to replace the templates without changing your Python code!

Customizable Architecture

PRGA features a highly customizable FPGA architecture at various levels. You are also welcome to bring your own designs or any third-party/proprietary IPs into your custom FPGAs!

ASIC-friendly RTL

PRGA-generated RTL is highly ASIC-friendly, both for implementation, characterization, and verification.

Incremental Verification

From behavioral simulation, to post-synthesis, LUT-based simulation, all the way to post-implementation simulation, PRGA features automated, incremental verification.

Princeton Reconfigurable Gate Array

Design, customize, and build your own FPGA!

- Study FPGA architecture with accurate, gate-level timing, area and power characterization.

- Research novel configuration protocol, e.g. partial reconfiguration, dynamic reconfiguration, multi-context FPGA, and secure bitstream!

- Integrate an open-source embedded FPGA IP in your next SoC design!

- And more…

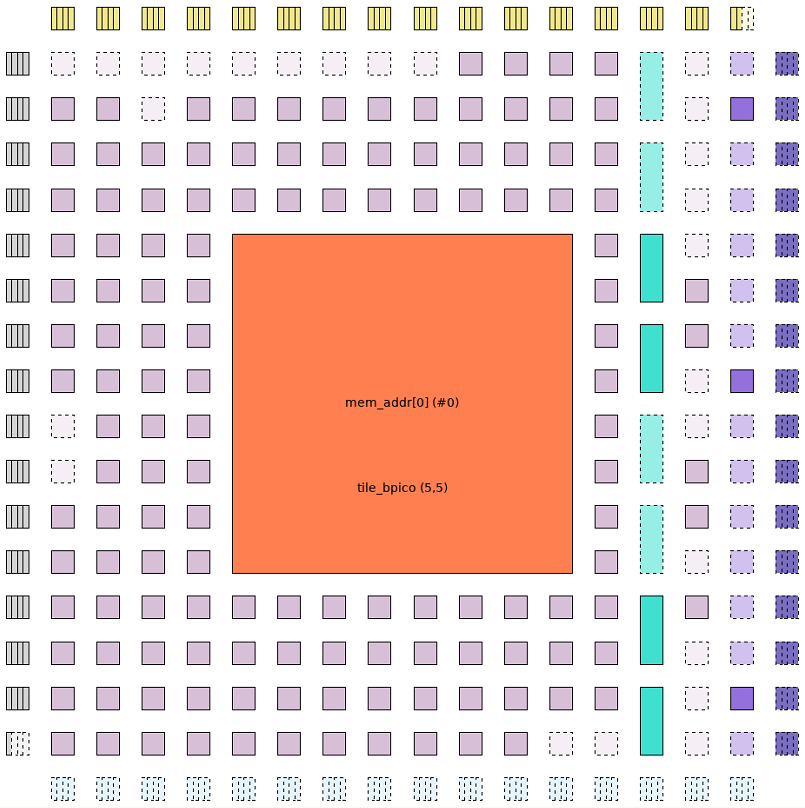

Bring Your Own IPs into the Heterogeneous Architecture

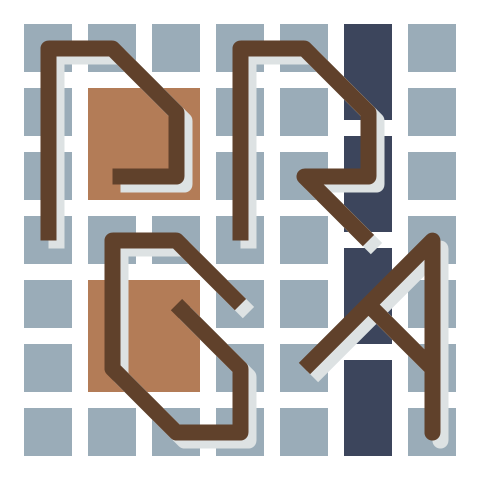

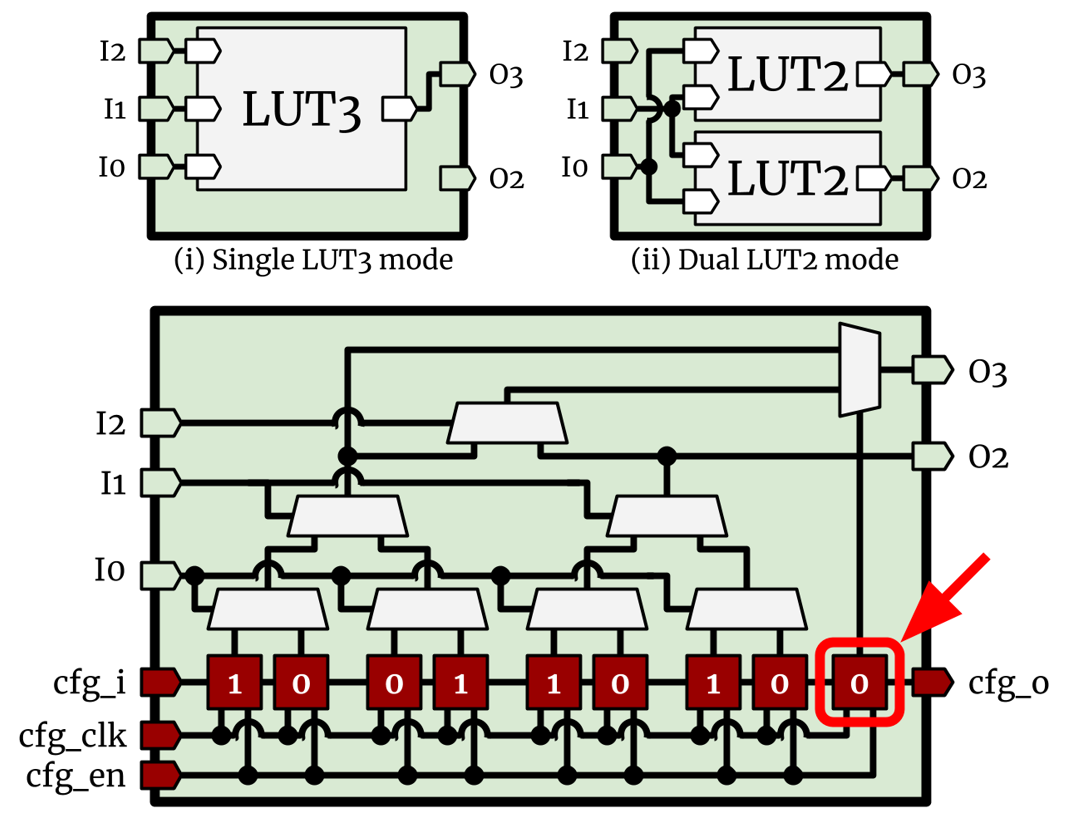

Multi-Modal Primitives

Increase the utilization rate of gates with multi-modal primitives.

LUT3= 2LUT2s with shared inputs- 8Kbit RAM can be used as

256x64b,512x32b,1024x16b, … - Also feel free to design your own multi-modal primitives!